CMOS

CMOS, també conegut com a Metall Òxid Semiconductor Complementari (de l'anglès: Complementary Metal Oxide Semiconductor, CMOS) és una tecnologia per a la construcció de circuits integrats. La tecnologia CMOS es fa servir en microprocessadors, microcontroladors, SRAM i en circuits de lògica digital, i també en circuits analògics com sensors d'imatge, circuits de conversió i transceptors integrats per a diferents tipus de comunicació. La tecnologia CMOS va ser patentada per Frank Wanlass el 1967 (US patent 3,356,858).

La tecnologia CMOS també és anomenada complementary-symmetry metal–oxide–semiconductor (o COS-MOS[1])

Les dues característiques més importants de la tecnologia CMOS són l'alta immunitat al soroll i el baix consum energètic en repòs. Aquesta última característica es deu a la utilització conjunta de transistors PMOS i NMOS de tal manera que només hi ha consum energètic quan hi ha un canvi de sortida i, en repòs, als corrents paràsits. D'aquesta manera, els dispositius construïts amb tecnologia CMOS tenen un baix escalfament, no com altres tecnologies digitals com la tecnologia TTL (transistor-transistor lògic) o lògica NMOS, que utilitzen dispositius amb lògica de canal n.

La tecnologia CMOS permet una gran miniaturització, de manera que és possible la integració d'una alta densitat de funcions lògiques en un sol integrat. Aquest va ser el motiu principal per qual la tecnologia CMOS va convertir-se en la dècada dels anys vuitanta la tecnologia més utilitzada per implementar circuits integrats a molt gran escala.

La frase «Metall-Òxid-Semiconductor» fa referència a l'estructura física amb la qual certs transistors d'efecte de camps són construïts. Aquests transistors tenen una porta de metall situada a sobre d'un aïllant d'òxid, que es troba a sobre d'un material semiconductor. Al principi es feia servir l'alumini com a metall però va ser substituït pel silici policristal·lí (que técnicament es un semiconductor i no pas un metall).

Detalls tècnics

Els circuits CMOS són circuits en els quals es combinen transistors MOSFET de tipus P i N (PMOS i NMOS) per implementar portes lògiques, circuits digitals i els seus processos per a la implementació en circuits integrats, que es poden trobar en ordinadors, equips de telecomunicacions i equips de processament de senyal. Malgrat que la lògica CMOS es pot implementar en dispositius discrets, els productes comercials CMOS estan integrats per milions (o centenars de milions) de transistors d'ambdós tipus en peces rectangulars de silici d'entre 10 i 400 mm². Aquests dispositius són anomenats xips, o integrats.

Els circuits CMOS dissipen menys potència que les famílies lògiques que utilitzen càrregues resistives, de manera que predominen en els circuits integrats actuals.[2]

La característica que diferencia els circuits CMOS és que estan construïts de tal manera que tots els transistors PMOS tinguin una entrada des de la font d'alimentació o des de la sortida d'un altre transistor PMOS. De la mateixa manera, els transistors NMOS tenen connectat a l'entrada el node de massa o un altre transistor NMOS. D'aquesta manera, en els circuits CMOS digitals, el subcircuit de transistors PMOS s'anomena de pull-up i es fa servir per aconseguir un valor de tensió alt (en binari 1), i el subcircuit de transistors NMOS s'anomena de pull-down i es fa servir per aconseguir un valor de tensió baix (en binari 0). La composició dels transistors PMOS crea una baixa resistència elèctrica entre surtidor i drenador quan a la porta s'hi aplica baixa tensió, i una alta resistència quan la tensió de porta té un valor elevat. Per l'altra banda, la composició dels transistors NMOS crea una alta resistència entre surtidor i drenador quan s'aplica una baixa tensió a la porta, i una baixa resistència quan a la porta s'hi aplica alta tensió.

La tecnologia CMOS utilitza aquest antagonisme entre transistors PMOS i NMOS per fer-los treballar en parelles per a construir funcions lògiques. Així, per a la construcció d'una porta porta NOT es connecten les dues portes i els dos drenadors d'un transistor PMOS i un NMOS. D'aquesta manera, una tensió alta a les portes provoca que el MOSFET N condueixi i el MOSFET P no condueixi, i complementàriament s'aconsegueix el contrari amb un nivell baix de tensió a les portes. Durant la commutació, el voltatge de drenador canvia d'un valor a l'altre, fent que aquest sigui l'únic moment en què els dos transistors condueixen alhora. Aquesta combinació redueix el consum energètic i la generació de calor.

Funcionament de la inversió de senyal amb tecnologia CMOS

Si ens fixem en la imatge de la dreta, podem veure un transistor PMOS (transistor de dalt) i un transistor NMOS (transistor de baix) connectats com s'ha esmentat a l'apartat anterior.

- Quan a l'entrada (node A) tenim un voltatge baix (nivell lògic 0), el transistor NMOS té una alta resistència entre drenador i surtidor (es troba en tall), i el transistor PMOS té una baixa resistència (conducció), de manera que a la sortida (node Q) tindrem el valor de tensió Vdd (valor 1).

- Quan a l'entrada (node A) tenim un voltatge alt (nivell lògic 1), el transistor NMOS té una baixa resistència entre drenador i surtidor (es troba en conducció), i el transistor PMOS té una resistència alta (tall), de manera que a la sortida (node Q) tindrem el valor de massa (valor 0).

Una altra de les característiques importants dels circuits CMOS és que són regeneratius: un senyal degradat que escometi una porta lògica CMOS serà restaurat al seu valor lògic inicial 0 o 1, sempre que encara estigui dins dels marges de soroll que el circuit pugui tolerar.

Consideracions de disseny: dualitat

Una característica important dels circuits CMOS és la dualitat que existeix entre els transistors PMOS i NMOS. Un circuit CMOS es crea per permetre que a la sortida sempre existeixi una connexió a la font de tensió o a la massa. Per aconseguir això, totes les rutes d'accés a la font d'alimentació han d'estar complementades per les d'accés a massa. Per aconseguir això, degut a la llei de De Morgan, tots els transistor PMOS en paral·lel han de tenir transistor NMOS en sèrie, i tots els transistors PMOS en sèrie han de tenir transistors NMOS en paral·lel per complementar els accessos esmentats, de manera que en el circuit ha d'haver el mateix nombre de transistors NMOS que PMOS.

Lògica

Altres funcions lògiques com la porta AND o la porta OR requereixen altres estructures de connexió dels transistors.[3]

- Porta AND: L'estructura CMOS de la porta AND consisteix en dos transistors NMOS connectats en sèrie, dos transistors PMOS connectats en paral·lel i un inversor a la sortida.

- Porta OR: L'estructura CMOS de la porta OR consisteix en dos transistors NMOS connectats en paral·lel, dos transistors PMOS connectats en sèrie i un inversor a la sortida.

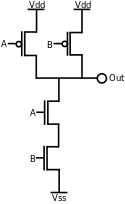

La imatge de la dreta mostra el circuit d'una porta NAND en lògica CMOS. Si les dues entrades A i B tenen un nivell alt, els dos transistors NMOS (a la part inferior de la imatge) es troben en conducció, mentre que els transistors PMOS (a la part superior de la imatge) es troben en tall, de manera que la sortida estarà connectada a Vss (massa), que donarà una sortida de nivell baix. Si qualsevol de les dues entrades A o B tingués un nivell baix, un dels transistors NMOS no conduiria i un dels transistors PMOS si, de manera que hi hauria una connexió del node de sortida amb el node a tensió Vdd (tensió d'alimentació), obtenint un nivell alt.

L'avantatge de la tecnologia CMOS envers la NMOS és que tant les transicions de nivell baix a alt i d'alt a baix són més ràpides perquè els transistors de pull-up (PMOS) tenen, perquè els portadors majoritaris són els forats, menor resistència quan estan en commutació, el contrari que les resistències de càrrega en la tecnologia NMOS. A més a més, el senyal de sortida mostra un rang de tensió de sortida menor (tensió d'alimentació i massa). Aquesta simetria fa que la tecnologia CMOS sigui més resistent al soroll.

Exemple: porta NAND en disseny físic

Aquest exemple mostra la porta lògica NAND en una representació del seu nivell físic tal com estaria fabricat vist des de dalt. El circuit està construït sobre un substrat tipus P. La polisilicona, la difusió i la porta N estan referides com capes base i s'introdueixen dins del substrat tipus P. Els contactes travessen una capa aïllant entre les capes i la capa de metall per a fer la connexió.

Les entrades a la porta NAND (en verd a la imatge) són polisilicona. Els transistors CMOS estan formats per la intersecció de la polisilicona i la difusió: difusió N per al dispositiu N, difusió P per al dispositiu P (en color salmó i groc respectivament a la imatge). La sortida (out) es connecta junt al metall (blau clar). La connexió entre el metall i la polisilicona o la difusió són fetes a través dels contactes (il·lustrat amb quadrats negres). El disseny de la placa descrit coincideix amb la imatge del circuit NAND anterior.

El transistor tipus N es fabrica en substrat tipu P. El transistor tipus P es fabrica en una porta tipus N. El substrat tipus P es connecta a Vss i la porta tipus N es connecta a Vdd per evitar el latch-up.

CMOS analògic

A més de les aplicacions digital, la tecnologia CMOS també es fa servir en aplicacions d'electrònica analògica degut a dues característiques importants dels transistors MOSFET:

- Alta impedància d'entrada: La porta d'un transistor MOS, degut a la capa d'òxid, té el funcionament equivalent d'un condensador, de manera que no hi ha corrent de polarització com en un transistor bipolar.

- Baixa resistència de canal.

Per això la tecnologia CMOS es fa servir en diferents camps de l'electrònica analògica:

- Amplificadors operacionals: en els quals destaquen els amplificadors Rail-to-Rail en els quals el marge de tensió de sortida va des de l'alimentació positiva a la negativa.

- Reguladors de tensió: gràcies a la característica de baixa dissipació de calor.

- Fonts commutades

- Aplicacions de telecomunicacions: També es fa servir la tecnologia CMOS per circuits de radiofreqüència, concretament a freqüències de microones, en els blocs de mesclat de senyal (analògic+digital).

Rang de temperatura

Els dispositius CMOS convencionals poden treballar en un rang d'entre −55 °C to +125 °C. L'agost de 2008 van sortir a la llum estudis teòrics que asseguraven que els transistors CMOS de silici poden treballar a temperatures inferiors a 40 K, or −233 °C.[4] De fet fer treballar dispositius a temperatures properes a 40 K s'ha aconseguit utilitzant un processador AMD Phenom II amb overclock amb una combinació de nitrogen líquid i heli.[5]

Potència: commutació i pèrdues

La tecnologia CSMOS dissipa menys potència que la tecnologia NMOS perquè CMOS dissipa potència només durant la commutació. En una aplicació ASIC en un procés modern de 90 nanometres, la commutació de la sortida triga aproximadament 120 picosegons, i això succeeix cada 10 nanosegons. La lògica NMOS dissipa potència potència encara que la seva sortida estigui en nivell baix, perquè hi ha corrent que va des de Vdd a Vss a través de la resistència de càrrega en una xarxa de tipus N.

Els circuits CMOS dissipen potència amb la càrrega de les capacitats paràsites (generalment degudes a la porta i la capacitat del cablejat, però també al drenador i a sortidor) encara que ja hagin commutat. La càrrega moguda és la capacitat multiplicada per la variació de tensió. Multiplicant aquest valor per la freqüència de commutació a les capacitats de càrrega s'aconsegueix el corrent utilitzat, i multiplicant pel voltatge un altre cop aconseguim la potència dissipada pels dispositius CMOS:

Una altra forma de consum de potència va començar a aparèixer a la dècada del 1990, a mesura que el cablejat dels integrats es feia més estret i els cables augmentaven la seva resistència. Les portes CMOS al final d'aquest cablejat endarrereixen les transicions d'entrada. Durant aquestes transicions, tant les xarxes NMOS com PMOS condueixen parcialment, i el corrent va directe des de Vdd a Vss.

Tant els transistors PMOS com NMOS tenen un llindar de tensió porta-surtidor per sota del qual el corrent a través del dispositiu cau exponencialment. Històricament, els dissenys CMOS que treballen a tensions d'alimentació majors que la seva tensió llindar(Vdd ha de ser 5 V, i Vth per NMOS i PMOS ha de ser700 mV). Un tipus especial de transistor CMOS amb una tensió llindar propera a zero és el transistor natiu.

Propietats

La família lògica té una sèrie d'avantatges que la fan superior a unes altres en la fabricació de circuits integrats digitals:

- El baix consum de potència estàtica, gràcies a l'alta impedància d'entrada dels transistors de tipus MOSFET i que, en estat de repòs, un circuit CMOS només experimentarà corrents paràsits. Això és degut al fet que en cap dels dos estats lògics existeix un camí directe entre la font d'alimentació i el terminal de terra.

- Gràcies al seu caràcter regeneratiu, els circuits CMOS són robusts enfront de soroll o degradació de senyal a causa de la impedància del metall d'interconnexió.

- Els circuits CMOS són senzills de dissenyar.

- La tecnologia de fabricació està molt desenvolupada, i és possible aconseguir densitats d'integració molt altes a un preu molt menor que altres tecnologies.

Alguns dels inconvenients són els següents:

- A causa del caràcter capacitiu dels transistors MOSFET, i al fet que aquests són emprats per duplicat en parelles NMOS-PMOS, la velocitat dels circuits CMOS és comparativament menor que la d'altres famílies lògiques.

- Són vulnerables a latch-up: Consisteix en l'existència d'un tiristor paràsit en l'estructura CMOS que entra en conducció quan la sortida supera l'alimentació. Això es produïx amb relativa facilitat a causa de la component inductiva de la xarxa d'alimentació dels circuits integrats. El latch-up produïx un camí de baixa resistència al corrent d'alimentació que implica la destrucció del dispositiu. Seguint les tècniques de disseny adequades aquest risc és pràcticament nul. Generalment és suficient amb espaiar contactes de substrat i pous de difusió amb suficient regularitat, per a assegurar-se que està sòlidament connectat a massa o alimentació.

- Segons es va reduint la grandària dels transistors, els corrents paràsits comencen a ser comparables als corrents dinàmics (degudes a la commutació dels dispositius).

Referències

- ↑ COS-MOS és una marca patentada de RCA, de manera que altres fabricants van ser forçats a trobar un altre nom—CMOS

- ↑ Baker, R. Jacob. CMOS: circuit design, layout, and simulation. Second. Wiley-IEEE, 2008, p. 1080. ISBN 978-0-470-22941-5.

- ↑ http://www.allaboutcircuits.com/vol_4/chpt_3/7.html

- ↑ Edwards C, "Temperature control", Engineering & Technology Magazine 26 July - 8 August 2008, IET

- ↑ Patrick Moorhead. «Breaking Records with Dragons and Helium in the Las Vegas Desert». blogs.amd.com/patmoorhead, 15-01-2009. Arxivat de l'original el 2012-07-07. [Consulta: 18 setembre 2009].

Vegeu també

Bibliografia

- Baker, R. Jacob. CMOS: Circuit Design, Layout, and Simulation, Third Edition. Wiley-IEEE, 2010, p. 1174. ISBN 978-0-470-88132-3. http://CMOSedu.com

- Weste, Neil H. E. and Harris, David M.. CMOS VLSI Design: A Circuits and Systems Perspective, Fourth Edition. Boston: Pearson/Addison-Wesley, 2010, p. 840. ISBN 978-0-321-54774-3. http://CMOSVLSI.com/

- Veendrick, Harry J. M.. Nanometer CMOS ICs, from Basics to ASICs. Nova York: Springer, 2008, p. 770. ISBN 978-1-4020-8332-7.

- Mead, Carver A. i Conway, Lynn. Introduction to VLSI systems. Boston: Addison-Wesley, 1980. ISBN 0-201-04358-0.