클럭 신호

클럭 신호(영어: clock signal)는 논리상태 H(high,논리 1)와 L(low,논리 0)이 주기적으로 나타나는 방형파(square wave) 신호를 말한다.

많은 경우 전자공학의 디지털 회로에서 클럭 신호에 맞추어 신호의 처리를 하는 동기 처리를 위해 사용한다. 클럭은 순차회로(sequential circuit)의 플립플롭(flip-flop)에서 반드시 필요하다. 여러개의 플립플롭이 비동기 클럭(asynchronous clock)으로 동작하더라도 클럭입력(clock input)은 필요하다. 논리 회로가 커지면 여러 개의 클럭이 필요하므로 동기식(synchronous)와 비동기식(asynchronous)이 섞여 설계되어 동작한다. FPGA와 같은 큰 회로에서는 클럭 신호가 별도로 지정하는 경우도 있다.[1] 별도의 클럭 입력이 결정되어 있고, 내부에서 클럭 네트워크를 통해 각 논리 모듈로 전용 신호선이 존재한다.

클럭 신호의 요소는:

- 신호의 크기

- 주기를 결정하는 주파수

- 한 주기 동안 상태 H와 L의 시간비인 듀티비

가 있다.

클럭 신호는 디지털회로에서 많이 사용하므로 신호의 크기는 전압으로 나타난다. 디지털회로에서 전압은 보통 논리 게이트의 전압과 같게 설계한다. 전압상태의 기준은 0V(ground)을 L 상태로 Vcc을 H 상태로 발생 시키는 것이 보통이다. H는 5V, 3.3V 등 논리 게이트에 따라 다르고 처음 칩 설계시 고정되어 있다. 초기에 5V을 많이 사용하였으나 3.3V 등으로 낮아지는 경향이 있다.

주파수는 디지털 회로 설계 요구사항에 따라 결정하는 것이 일반적이다. 규모가 있는 디지털 회로는 보통 다양한 주파수가 필요한 경우가 발생하는데, 내부의 카운터 회로에 의해 주파수 변환하여 사용한다. 따라서 필요한 가장 빠른 주파수를 수정 발진기(crystal oscillator)를 사용하여 만들고 이것으로 분배한다. 수정 발진기의 발진 주파수 보다 빠른 경우 위상동기회로(PLL) 방식의 회로 구성을 통해 칩 내부에서 높은 주파수를 발진하여 사용한다.

클럭 신호에서 한 주기 동안 H와 L의 시간차비인 듀티비가 보통 50%인 방형파를 많이 사용한다. 디지털 회로에서 신호가 반영하는 시점은, 신호의 상태 변화할 때의 짧은 순간에 이루어지는 경우가 많다. 상태 L에서 H로 변화하는 순간인 상승에지(rising edge)나 H에서 L로 변하는 하강에지(falling edge)에서 동작하는 경우가 많다. 플립플럽은 상승 또는 하강에지에서 입력이 출력에 반영된다. 보통 마이크로프로세서에서는 듀티비가 50%을 많이 사용하지만, 경우에 따라 50%가 아닌경우도 있다:

- 듀티비 50% 유사, 이상형 클럭(two-phase clock) : 6809[3]

6809는 듀티비가 50%에서 약간의 시간차가 있어도 된다. 수정발진기를 사용하여 하나의 주파수를 만들고, 칩 내부에서 2개의 상(phase)이 다른 클럭을 만든어 CPU 내부에서 사용하고 밖으로도 출력한다.

DDR SDRAM은 상승에지 또는 하강에지에서 동기되어 데이터의 액세스가 처리된다. 디지털회로의 카운터 같은 경우, 각 플립플럽의 동작을 같은 시간에 하기 위한 동기 신호로 사용한다.

클럭은 두 개 이상의 디지털 회로의 동작을 통합하는 데에 쓰이는 신호이다. 동기화를 위해 클록 신호를 사용하는 회로는 갑자기 오르는 부분, 갑자기 떨어지는 부분에서 활발할 수 있다. 이를테면 DDR SDRAM은 두 곳에서 모두 활발해진다.

클럭 신호 발진

디지털 회로에 사용하는 클럭의 발생은 수정 발진기(quartz crystal oscillator, 또는 수정 발진자라고도 함)에 의해 만들어지는 경우가 대부분이다. 수정 발진자는 수정을 가공하여 박편을 만들어 양극에 특정 정해진 주파수를 입력하면 자기의 고유 주파수만을 걸러내어 고유의 주파수를 발생시키는 소자이다. 입력된 주파수를 자기의 공진 주파수가 되도록 유도하는 방식으로 클럭이 발생한다. 수정 발전자는 가공 방식과 크기에 따라 주파수가 달라지지만 너무 낮은 주파수나 너무 높으면 발생에 한계가 있다.

수정 발진기 자체에 직류 전압을 인가하면, 클럭 신호가 발생되지 않는다. 따라서 정해진 발진기의 주파수 근처의 방형파를 만드는 전자회로를 이용하여 수정 발진기에 신호를 인가하면 수정 발진기는 자기 고유의 주파수만 공진 시켜 전자회로가 해당 주파수로 공진하도록 하는 유도 역할을 한다. 결국 전자회로와 결합하여 발진회로가 완성된다.

클럭 신호를 발진하면 이상적인 방현파가 불가능하다. 상승 또는 하강 엣지에서 상태 변화 시간이 필요하다.

마이크로프로세서에서 클럭 신호 발진

| 전원 인가형 자체 발진 | 발진 회로와 결합한 수정 발진자 |

|---|---|

|

|

클럭 신호 발생 부품 자체에 발진회로와 수정 발진자를 결합하여 하나의 부품으로 만들 수 있다. 이에 비해 발진회로 없이 수정 발진 자체만 기능하는 부품도 있어 선택적으로 사용할 수 있다.

수정 발진자와 그 부가 회로를 넣어 하나의 부품을 제작하고 Vcc-GND 전원을 인가하면 클럭 신호가 나온다. 따라서 수정 발진자에 필요한 주파수 발생회로가 PCB내에 별도로 추가할 필요가 없다. 그러나 수정 발진 기능만 하는 부품은 수정 발진자에 클럭을 인가하기 위한 회로와 부가 회로가 필요하다. 현실적으로 클럭을 발생하는 회로는 그리 어렵지 않다. 단지 콘덴서를 반도체 부품에 넣는 것이 부담 스럽기 때문에 20p 정도의 콘덴서 2개와 필요에 따라 저항 하나 정도면 반도체 내의 발진회로와 PCB의 발진회로가 결합하여 발진회로 전체를 구성할 수 있다. 그래서 마이크로컨트롤러 등에는 수정발진 기능만 있는 부품을 많이 사용한다.

피어스 발진 회로

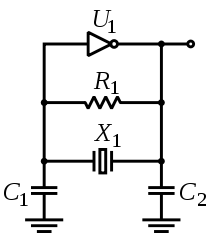

피어스[4][5]에 의해 만들어진 피어스 발진회로(Pierce oscillator)는 디지털 회로에 사용하는 NOT 게이트와 수정 발진자, R 그리고 C를 활용하여 쉽게 만들 수 있다. 콜피츠 발진기(Colpitts oscillator)의 파생 회로이다.

수정 발진자의 활용

수정 발진자를 사용한 다음과 같은 회로를 통해 클럭을 얻을 수 있다:

NOT 게이트 같은 논리 회로와 R-C의 조합으로 수정 발진자에 정해진 주파수 근처를 인가하면 수정 발진자의 정해진 특정 주파수로 공진하게 할 수 있다. 공진이 되면 해당 주파수가 출력 된다. 보통 수정 발진자 없이, 능동 소자와 R-L-C 등을 사용한 발진회로로 주파수를 만들 수 있으나 각 소자의 오차 등으로 인하여 정확한 주파수를 얻을 수 없다.

위상동기회로를 사용한 클럭 신호 발진

낮은 주파수의 수정발진기를 사용하여 높은 주파수를 얻는 방법으로 위상동기회로(PLL) 방식의 회로 구성으로 얻는다.

위상동기회로는 통신 등 여러 응용분야에서도 사용하지만, 임베디드 CPU의 고속 클럭 발생회로에서도 사용한다.

임베디드 CPU의 많은 경우 높은 동작 주파수는 PLL을 사용하는 경우가 많다.[6] 그리고 위상동기회로를 사용할 경우 디지털 회로의 구성요소의 카운터값을 바꾸면 다른 주파수를 만들 수 있다는 장점도 있다. 수정발진기 주파수 입력 FI이 고정된 상태에서 PLL의 되먹임 카운터 N을 프로그램 방식으로 조절하면 출력 주파수 FO는 다른 주파수를 얻을 수 있다.

이더넷 카드에 들어가는 디지털회로는 25MHz로부터 DPLL을 사용하여 원하는 주파수의 클럭을 만들어 사용한다.[7] 상대방에서 보내온 데이터 신호로부터 데이터를 추출하기 위해서는 데이터의 비트 시작과 끝 시간을 알아야 하는데 25MHz로 클럭 신호로부터 DPLL을 사용하여 동기 클럭 신호를 얻는다.

같이 보기

각주

- ↑ “Spartan-3 FPGA Family Data Sheet” (PDF). 《Spartan-3 사용 설명서》 (영어). http://www.xilinx.com. June 27,2013. 2013년 9월 17일에 확인함.

|출판사=에 외부 링크가 있음 (도움말) - ↑ “Z80 Family CPU User Manual” (PDF). 《Z80 사용 설명서》 (영어). www.zilog.com. 2004. 2013년 9월 17일에 확인함.

- ↑ “MC6809 8-Bit Microprocessing Unit” (PDF). 《MC6809 사용 설명서》 (영어). Motorola Microprocessor Data. 2004. 2013년 9월 17일에 확인함.

- ↑ Pierce, George W. (October 1923), “Piezoelectric crystal resonators and crystal oscillators applied to the precision calibration of wavemeters”, 《Proceedings of the American Academy of Arts and Sciences》 59 (4): 81–106, doi:10.2307/20026061

- ↑ 《Electrical System》

- ↑ 삼성전자(주) (2004년 6월 30일). 《S3C2440A 32-BIT RISC MICROPROCESSOR USER'S MANUAL》. CLOCK & POWER MANAGEMENT.

- ↑ “Phase Locked Loop”. 《gorry》. http://www.erg.abdn.ac.uk.

|publisher=에 외부 링크가 있음 (도움말)