Architektura DLX

Architektura DLX (wym. Deluxe) – architektura procesora typu RISC, zaprojektowana w latach 90. przez Johna Hennessy’ego oraz Davida Pattersona – głównych twórców architektur odpowiednio Stanford MIPS i Berkeley RISC. DLX jest 32-bitową, zmodyfikowaną i uproszczoną wersją architektury MIPS. Została stworzona głównie w celach dydaktycznych i jest wykorzystywana w ramach akademickich kursów architektury i organizacji komputerów, najczęściej z wykorzystaniem symulatorów, przedstawiających graficznie etapy potoku oraz interpretujących programy asemblerowe.

Format rozkazów

W architekturze DLX wyróżnia się trzy formaty rozkazów: R-type, I-type oraz J-type. We wszystkich rozkazów musi zostać określony kod operacji, natomiast format pozostałej części rozkazu zależy od jego rodzaju.

Rozkazy typu R (ang. register) działają na trzech rejestrach: dwóch rejestrach źródłowych (rs1, rs2) oraz jednym rejestrze docelowym (rd):

Rozkazy typu I (ang. immediate) określają dwa rejestry: jeden źródłowy (rs1) i jeden docelowy (rd) oraz 16-bitową wartość „natychmiastową”:

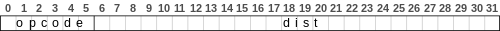

Rozkazy typu J (ang. jump) są natomiast rozkazami skoku i oprócz kodu operacji zawierają 26-bitowy operand, z którego wyznaczany jest adres docelowy.

Kody operacji mają długość 6 bitów, co pozwala na określenie w sumie 64 możliwych rozkazów.

Rejestry

Komputer DLX składa się z trzydziestu dwóch 32-bitowych rejestrów całkowitoliczbowych oraz 32 rejestrów zmiennoprzecinkowych, które mogą być wykorzystywane jako rejestry 32-bitowe (pojedynczej precyzji) lub parami F0–F1, F2–F3 itd. jako rejestry 64-bitowe (podwójnej precyzji).

Potokowość

Podobnie jak architektura MIPS, DLX wykorzystuje przetwarzanie potokowe. W celu usprawnienia wykonywania programu, stosowana jest także technika forwardingu. Potok składa się z pięciu faz:

- pobranie rozkazu – ang. instruction fetch (IF),

- zdekodowanie rozkazu/pobranie zawartości rejestrów – ang. instruction decode/register fetch (ID),

- wykonanie rozkazu/wyznaczenie adresu – ang. execute/address calculation (EX),

- dostęp do pamięci – ang. memory access (MEM),

- zapis do rejestrów – ang. write back (WB).

Bibliografia

- Ethan Miller: The DLX Processor, csee.umbc.edu (ang.) [data dostępu: 2021-02-01].

- Gurpur M. Prabhu: DLX Architecture, web.cs.iastate.edu (ang.) [data dostępu: 2021-02-01].

Linki zewnętrzne

- WinDLX – implementacja architektury DLX dla 16-bitowych systemów Windows. mr.inf.tu-dresden.de. [zarchiwizowane z tego adresu (2007-07-07)]. (niem.).